### **User Manual**

# 3162A/B

## 500 MS/s (SINGLE OR DUAL CHANNEL) WAVEFORM SYNTHESIZER

Publication No. 980818

#### RACAL INSTRUMENTS

#### Racal Instruments, Inc.

4 Goodyear St., Irvine, CA 92618-2002 Tel: (800) RACAL-ATE, (800) 722-2528, (949) 859-8999; FAX: (949) 859-7139

#### Racal Instruments, Ltd.

480 Bath Road, Slough, Berkshire, SL1 6BE, United Kingdom Tel: +44 (0) 1628 604455; FAX: +44 (0) 1628 662017

#### Racal Systems Electronique S.A.

18 Avenue Dutartre, 78150 LeChesnay, France Tel: +33 (1) 3923 2222; FAX: +33 (1) 3923 2225

#### Racal Systems Elettronica s.r.l.

Strada 2-Palazzo C4, 20090 Milanofiori Assago, Milan, Italy Tel: +39 (0)2 5750 1796; FAX +39 (0)2 5750 1828

#### Racal Elektronik System GmbH.

Technologiepark Bergisch Gladbach, Friedrich-Ebert-Strasse, D-51429 Bergisch Gladbach, Germany Tel.: +49 2204 8442 00; FAX: +49 2204 8442 19

#### Racal Australia Pty. Ltd.

3 Powells Road, Brookvale, NSW 2100, Australia Tel: +612 9936 7000, FAX: +612 9936 7036

#### Racal Electronics Pte. Ltd.

26 Ayer Rajah Crescent, 04-06/07 Ayer Rajah Industrial Estate, Singapore 0513. Tel: +65 7792200, FAX: +65 7785400

#### Racal Instruments, Ltd.

Unit 5, 25F., Mega Trade Center, No 1, Mei Wan Road, Tsuen Wan, Hong Kong, PRC Tel: +852 2405 5500, FAX: +852 2416 4335

http://www.racalinstruments.com

RACAL

**PUBLICATION DATE: May 8, 2001**

Copyright 2001 by Racal Instruments, Inc. Printed in the United States of America. All rights reserved. This book or parts thereof may not be reproduced in any form without written permission of the publisher.

#### WARRANTY STATEMENT

All Racal Instruments, Inc. products are designed and manufactured to exacting standards and in full conformance to Racal's ISO 9001 procedures.

For the specific terms of your standard warranty, or optional extended warranty or service agreement, contact your Racal customer service advisor. Please have the following information available to facilitate service.

- 1. Product serial number

- 2. Product model number

- 3. Your company and contact information

You may contact your customer service advisor by:

E-Mail: Helpdesk@racalinstruments.com

Telephone: +1 800 722 3262 (USA)

+44(0) 8706 080134 (UK) +852 2405 5500 (Hong Kong)

Fax: +1 949 859 7309 (USA)

+44(0) 1628 662017 (UK) +852 2416 4335 (Hong Kong)

#### RETURN of PRODUCT

Authorization is required from Racal Instruments before you send us your product for service or calibration. Call your nearest Racal Instruments support facility. A list is located on the last page of this manual. If you are unsure where to call, contact Racal Instruments, Inc. Customer Support Department in Irvine, California, USA at 1-800-722-3262 or 1-949-859-8999 or via fax at 1-949-859-7139. We can be reached at:

helpdesk@racalinstruments.com.

#### PROPRIETARY NOTICE

This document and the technical data herein disclosed, are proprietary to Racal Instruments, and shall not, without express written permission of Racal Instruments, be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than Racal Instruments. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents which specify procurement of products from Racal Instruments.

## FOR YOUR SAFETY

Before undertaking any troubleshooting, maintenance or exploratory procedure, read carefully the **WARNINGS** and **CAUTION** notices.

This equipment contains voltage hazardous to human life and safety, and is capable of inflicting personal injury.

If this instrument is to be powered from the AC line (mains) through an autotransformer, ensure the common connector is connected to the neutral (earth pole) of the power supply.

Before operating the unit, ensure the conductor (green wire) is connected to the ground (earth) conductor of the power outlet. Do not use a two-conductor extension cord or a three-prong/two-prong adapter. This will defeat the protective feature of the third conductor in the power cord.

Maintenance and calibration procedures sometimes call for operation of the unit with power applied and protective covers removed. Read the procedures and heed warnings to avoid "live" circuit points.

Before operating this instrument:

- 1. Ensure the instrument is configured to operate on the voltage at the power source. See Installation Section.

- 2. Ensure the proper fuse is in place for the power source to operate.

- 3. Ensure all other devices connected to or in proximity to this instrument are properly grounded or connected to the protective third-wire earth ground.

#### If the instrument:

- fails to operate satisfactorily

- shows visible damage

- has been stored under unfavorable conditions

- has sustained stress

Do not operate until performance is checked by qualified personnel.

This page was left intentionally blank.

#### **Table of Contents**

| Chapter 1                        |      |

|----------------------------------|------|

| GETTING STARTED                  | 1-1  |

| What's In This Chapter           | 1-1  |

| Introduction                     | 1-1  |

| Options                          | 1-3  |

| Manual Changes                   | 1-4  |

| Safety Considerations            | 1-4  |

| Supplied Accessories             | 1-4  |

| Specifications                   | 1-4  |

| Functional Description           | 1-4  |

| Input and Output Connectors      | 1-4  |

| Main Output - Channel A          | 1-6  |

| Main Output -Channel B           | 1-6  |

| SYNC Output                      | 1-6  |

| Trigger/PLL/FSK Input            | 1-6  |

| AM/PM Input -Channel A           | 1-6  |

| AM Input - Channel B             | 1-7  |

| Reference Clock Input            | 1-7  |

| Frequency/ Segment Control Input | 1-7  |

| Operating Modes                  | 1-7  |

| Continuous Mode                  | 1-7  |

| Triggered Mode                   | 1-7  |

| Burst Mode                       | 1-8  |

| Gated Mode                       | 1-8  |

| Output Type                      | 1-8  |

| Standard (Fixed) Waveforms       | 1-8  |

| Arbitrary (User) Waveforms       | 1-8  |

| Sequenced Waveforms              | 1-9  |

| Synthesizer Agility              | 1-12 |

| Output State                     | 1-12 |

| Amplitude Modulation             | 1-12 |

| Front-Panel / VXIbus PLL         | 1-12 |

| Frequency Counter                | 1-13 |

| Dhaga Madulation                 | 4.40 |

| Filters                                          | 1-13 |

|--------------------------------------------------|------|

| Front Panel Indicators                           | 1-14 |

| Programming The Model 3162B                      | 1-14 |

| Chapter 2                                        |      |

| CONFIGURING The INSTRUMENT                       | 2-1  |

| Installation Overview                            | 2-1  |

| Unpacking and Initial Inspection                 | 2-1  |

| Safety Precautions                               | 2-1  |

| Performance Checks                               | 2-2  |

| Grounding Requirements                           | 2-2  |

| Long Term Storage or Repackaging For Shipment    | 2-2  |

| Preparation For Use                              | 2-3  |

| Logical Address Selection                        | 2-3  |

| Installation                                     | 2-4  |

| Chapter 3                                        |      |

| USING THE INSTRUMENT                             | 3-1  |

| Overview                                         | 3-1  |

| Inter-Channel Dependency                         | 3-1  |

| Output Termination                               | 3-1  |

| Input/Output Protection                          | 3-1  |

| Power On/Reset Defaults                          | 3-2  |

| What To Do Now                                   | 3-3  |

| Using the APPLy Command                          | 3-4  |

| Selecting the Active Channel                     | 3-7  |

| Output Configuration Commands                    | 3-8  |

| Selecting an Output Function Type                | 3-8  |

| Selecting a Standard Function Shape              | 3-9  |

| Changing the Frequency and Sample Clock          | 3-10 |

| Controlling Synthesizer Agility                  | 3-10 |

| FSK Mode                                         | 3-11 |

| HOP Mode                                         | 3-12 |

| Selecting the Reference Oscillator               | 3-13 |

| Programming the Output Amplitude and Offset      | 3-14 |

| Selecting the Filter                             | 3-14 |

| Activating the Backplane ECLTRG and TTLTRG Lines | 3-15 |

| Enabling the Main Output                         | 3-16 |

| Enabling the SYNC Output                         | 3-16 |

| Assigning the Source For The SYNC Output   | 3-1/        |

|--------------------------------------------|-------------|

| Selecting the SYNC Position                | 3-17        |

| Using the Built-In Standard Waveforms      | 3-18        |

| Selecting an Operating Mode                | 3-20        |

| Triggered Mode                             | 3-21        |

| Gated Mode                                 | 3-21        |

| Burst Mode                                 | 3-22        |

| Selecting the Trigger Source               | 3-23        |

| Using the Internal Trigger Generator       | 3-23        |

| Selecting the Trigger Slope                | 3-24        |

| Selecting the Trigger Level                | 3-24        |

| Using the Soft Trigger                     | 3-24        |

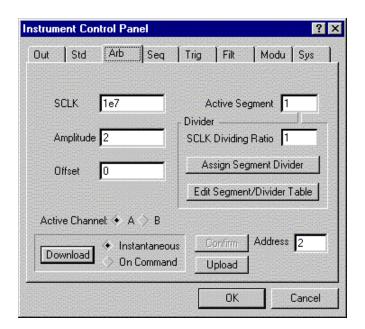

| Generating Arbitrary Waveforms             | 3-25        |

| What Are Arbitrary Waveforms?              | 3-25        |

| Arbitrary Memory Management                | 3-27        |

| Memory Management Commands                 | 3-27        |

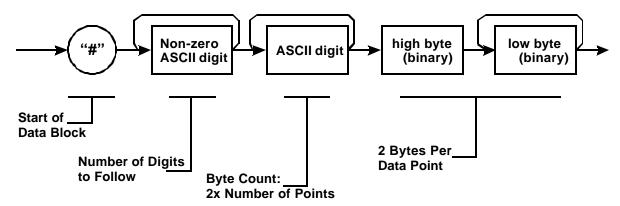

| Loading Arbitrary Waveforms                | 3-29        |

| Reversing Byte Order                       | 3-33        |

| Using Shared Memory                        | 3-33        |

| Generating Sequenced Waveforms             | 3-35        |

| What Are Sequenced Waveforms?              | 3-35        |

| Sequence Commands                          | 3-35        |

| Sequence Advance Commands                  | 3-36        |

| Sequence Advance Source Commands           | 3-37        |

| Front-Panel / VXIbus Phase Synchronization | 3-38        |

| PLL Commands                               | 3-39        |

| Using the Frequency Counter                | 3-40        |

| Using the Phase Modulation Input           | 3-40        |

| Inter-Channel Phase Control                | 3-41        |

| Amplitude Modulation Commands              | 3-41        |

| System-Related Commands                    | 3-42        |

| Chapter 4                                  |             |

| SCPI COMMAND REFERENCE                     | <i>∆</i> ₋1 |

| What's In This Chapter                     |             |

| Introduction To SCPI Language              |             |

| Command Format                             |             |

| Command Separator                          |             |

| The MIN and MAX Parameters                 |             |

| Querying Parameter Setting                 |             |

| Gaorying i diamotor county                 | 4-3         |

| Query Response Format                                           | 4-3  |

|-----------------------------------------------------------------|------|

| SCPI Command Terminator                                         | 4-3  |

| IEEE-STD-488.2 Common Commands                                  | 4-4  |

| SCPI Parameter Type                                             | 4-4  |

| Numeric Parameters                                              | 4-4  |

| Discrete Parameters                                             | 4-4  |

| Boolean Parameters                                              | 4-4  |

| Arbitrary Block Parameters                                      | 4-5  |

| SCPI Command Summary                                            | 4-5  |

| Output Configuration Command Summary                            | 4-10 |

| Standard Waveform Command Summary                               | 4-12 |

| Arbitrary Waveform, Sequence, and Shared Memory Command Summary | 4-13 |

| Modulation Command Summary                                      | 4-14 |

| Trigger Command Summary                                         | 4-14 |

| PLL Command Summary                                             | 4-14 |

| System-Related Command Summary                                  | 4-15 |

| IEEE-STD-488.2 Common Commands and Queries                      | 4-15 |

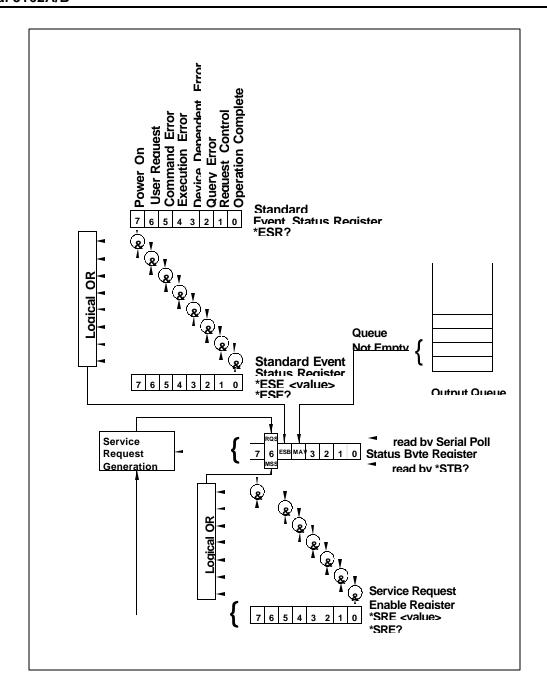

| The SCPI Status Registers                                       | 4-17 |

| The Status Byte Register (STB)                                  | 4-18 |

| Reading the Status Byte Register                                | 4-20 |

| Clearing the Status Byte Register                               | 4-20 |

| Service Request Enable Register (SRE)                           | 4-20 |

| Standard Event Status Register (ESR)                            | 4-20 |

| Standard Event Status Enable Register (ESE)                     | 4-21 |

| Error Messages                                                  | 4-22 |

| Device-Specific Commands                                        | 4-24 |

| Chapter 5                                                       |      |

| MAINTENANCE AND PERFORMANCE CHECKS                              | 5-1  |

| What's in This Chapter                                          | 5-1  |

| Disassembly Instructions                                        | 5-1  |

| Special Handling of Static Sensitive Devices                    | 5-2  |

| Cleaning                                                        | 5-2  |

| Repair and Replacement                                          | 5-3  |

| Performance Checks                                              | 5-3  |

| Environmental Conditions                                        | 5-3  |

| Warm-up Period                                                  | 5-3  |

| Initial Instrument Setting                                      | 5-4  |

| Recommended Test Equipment                                      | 5-4  |

|                                                                 |      |

| Performance Check Procedures                  | 5-4  |

|-----------------------------------------------|------|

| Frequency Accuracy                            | 5-5  |

| Amplitude Accuracy                            | 5-6  |

| DC Offset Characteristics                     | 5-7  |

| Square Wave Characteristics                   | 5-9  |

| Sine Characteristics                          | 5-10 |

| Sine Flatness                                 | 5-12 |

| Trigger Gate & Burst Characteristics          | 5-13 |

| Synthesizer Agility Characteristics           | 5-14 |

| PLL Characteristics                           | 5-16 |

| Adjustments                                   | 5-17 |

| Environmental Conditions                      | 5-17 |

| Warm-up Period                                | 5-17 |

| Recommended Test Equipment                    | 5-17 |

| Adjustment Procedures                         | 5-17 |

| Sample Clock Duty Cycle Adjustment            | 5-18 |

| Pulse Response Adjustment                     | 5-18 |

| Amplitude Adjustment                          | 5-20 |

| Offset Adjustment                             | 5-21 |

| PLL Adjustment                                | 5-22 |

| Troubleshooting                               | 5-22 |

| Recommended Test Equipment                    | 5-22 |

| Power-up Tests                                | 5-22 |

| Self-Test                                     | 5-23 |

| Main Board Circuits Checkout                  | 5-23 |

| Power Supply Checks                           | 5-24 |

| CPU and VXI ASIC Checks                       | 5-24 |

| Output Amplifier and Amplitude Control Checks | 5-25 |

| Clock Synthesizer Checks                      | 5-26 |

| Engine Board A/B Circuit Checkout             | 5-27 |

| Engine Board A/B Checks                       | 5-27 |

| Continuous Operation Checks                   | 5-27 |

| Triggered Operation Checks                    | 5-29 |

| D/A, Preamplifier & Amplitude Control Checks  | 5-29 |

| Sequence Generator Checks                     | 5-30 |

| Chapter 6                                     |      |

| PRODUCT SUPPORT                               | 6-1  |

| Product Support                               | 6-1  |

| Reshipment Instructions                       | 6-1  |

Support Offices......6-2

### **List of Figures**

| Figure 1-1, Model 3162A and 3162B                                      | 1-1  |

|------------------------------------------------------------------------|------|

| Figure 1-2, The Front Panel                                            | 1-5  |

| Figure 1-3, Segment 1 – Sin (x)/x Waveform                             | 1-9  |

| Figure 1-4,Segment 2 – Sine Waveform                                   | 1-10 |

| Figure 1-5. Segment 3 – Pulse Waveform                                 | 1-10 |

| Figure 1-6. Sequenced Waveforms                                        | 1-10 |

| Figure 1-7, WaveCAD Example                                            | 1-11 |

| Figure 2-1, Set Logical Address                                        | 2-4  |

| Table 3-1, Default Conditions After Power On or After *RST             | 3-2  |

| Table 3-1, Default Conditions After Power On or After *RST (continued) | 3-3  |

| Figure 3-3, WaveCAD Hop Table                                          | 3-12 |

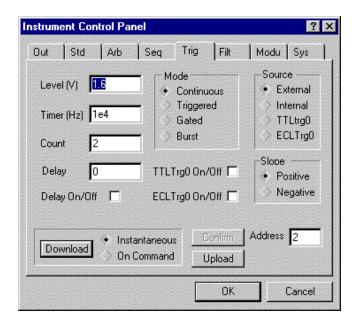

| Figure 3-5, WaveCAD Control Panel for Trigger Mode                     | 3-21 |

| Figure 3-6, WaveCAD's Arbitrary Waveform Control Panel                 | 3-26 |

| Figure 3-7, WaveCAD's Axis Definition Panel                            | 3-27 |

| Figure 3-8, Definite Length Arbitrary Block Data Format                | 3-30 |

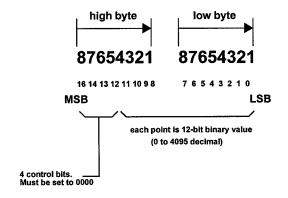

| Figure 3-9, 12-Bit Waveform Data Format                                | 3-30 |

| Table 5-1, CPU and VXI Interface Checks                                | 5-24 |

| Table 5.2 Output Amplifier and Amplitude Central Checks                | 5.25 |

This page was left intentionally blank.

# Chapter 1 GETTING STARTED

# What's In This Chapter

This chapter contains a general description of the VXIbus Model 3162A and 3162B Waveform Generators and an overall functional description of the instrument. It lists and describes various options available for these models. It also describes the front panel connectors and indicators.

This manual provides description of all features and options available with the instruments; however, some items described in the following paragraphs may not be installed in your instrument.

Figure 1-1, Model 3162A and 3162B

### Introduction

A detailed functional description is given following the general description of the features, functions, and options available with the Model 3162A and Model 3162B.

The Model 3162A is a VXIbus, single slot, C-size synthesized Waveform Generator. It is a high performance waveform generator that combines three powerful instruments in one small package: function generator, arbitrary waveform generator and sequence generator. The instrument provides a variety of standard waveforms to be used as test stimuli for different electronic devices.

The Model 3162B is a VXIbus, dual slot C-size, dual-channel synthesized

Revision 4/18/00

Waveform Generator. It has the same performance as the Model 3162A, except it has two separate main outputs. While sample clock, frequency, trigger and sequence modes are common to the two channels, each channel has separate controls for amplitude, offset, and waveform shape.

#### NOTE

The Model 3162B has the same functionality as the Model 3162A. This manual describes all functions and features that are available on the Model 3162B. If you own the Model 3162A, simply ignore all references in this chapter to the second output channel.

Despite its small size, the Model 3162B offers many features and functions such as *VXIpIug&play* compatibility, frequency hopping, amplitude modulation, FSK modulation, front panel or backplane PLL, phase modulation, counted burst, internal trigger-generator, and more. The instrument generates high quality, high accuracy waveforms throughout the specified frequency range, amplitude span and operating temperature.

The Model 3162B generates standard waveforms at frequencies ranging from  $100\mu Hz$  to 250 MHz. It can also generate arbitrary waveforms with clock rates ranging from 100mHz to 500 MHz. Clock rates and frequency may be set with 7 digits of resolution. The accuracy and the stability of the output frequency depend on the reference clock. As standard, a TCXO circuit provides 1ppm accuracy and stability. With the TCXO reference, the output frequency can be controlled to a full seven digits of resolution and accuracy.

Output amplitude may be programmed separately for each channel within the range of 20mV to 10Vp-p into an open circuit, and 10mV to 5V into  $50\Omega$ . Amplitude and offsets are programmed with 4 digits of resolution.

Using its PLL function, the generator can be phase locked to an external reference. An internal frequency counter detects the frequency of the external signal and adjusts the 3162B to its optimal lock-in range. After the instrument has locked, the phase offset between the two signals can be changed from 0° to +360°. Phase offset adjustment is controllable via SCPI commands or by using the PM input as a phase modulation control.

Besides its normal continuous mode, the Model 3162B responds to a variety of trigger modes. The output waveform may be gated, triggered, or may generate a counted burst of waveforms. A built-in trigger generator with a programmable period can be used as a replacement for an external trigger source.

The Model 3162B generates arbitrary waveforms with 12 bits of resolution. While ten standard waveforms are memory resident, up to 4096 additional waveforms may be downloaded from the controller to the instrument, using shared memory or standard data bus transfer. Waveforms may also be generated using the WaveCAD program.

The Model 3162B is a digital instrument. With the exception of standard waveforms, any waveform it generates must be first downloaded to waveform memory. The arbitrary waveform memory is a bank of 12-bit words. Each word

represents a point on the waveform. Each word has a horizontal address that can range from 0 to 1046464, and a vertical address that can range from -2047 to +2048 (12 bits). Using a high speed clocking circuit, the digital contents of the arbitrary waveform memory are extracted and routed to the Digital to Analog Converter (DAC). The DAC converts the digital data to an analog signal, and the output amplifier completes the task by amplifying or attenuating the signal at the output connector.

There is no need to use the complete memory bank every time an arbitrary waveform is generated. Waveform memory can be divided into up to 4096 smaller segments, and different waveforms can be loaded into each segment. The various segments may then be loaded into a sequence table to generate long and complex waveforms. The sequence table can link up to 4096 segments, while each segment can loop up to 1 million times.

The Model 3162B is fully programmable using SCPI commands and syntax. There are four ways to program the Model 3162B, the first being low-level programming of each individual parameter with SCPI commands. The second alternative is to use the *VXIplug&play* driver's Soft Front Panel (SFP) for high-level programming. The *SFP* driver simulates a mechanical front panel with the necessary push buttons, displays and dials to operate the Model 3162B as a bench-top instrument. The third way to program the 3162B is by using either the LabVIEW or LabWindows/CVI driver. The fourth way to program the 3162B is via the WaveCAD program. The Model 3162B will not operate without being programmed. Therefore, it is recommended that the user become familiar with its basic features, functions and programming concepts as described in this and the following chapters.

### **Options**

Revision 4/18/00

No options are offered for the generators. Compare the Model number with the number that is printed on the instrument to verify which of the instrument you received. Contact your nearest Racal representative if the number printed on the case does not reflect the correct version ordered. The list of available versions is given below:

- 407627-001 Model 3162A, 500MS/s Waveform Generator, w/1Meg RAM, 1PPM

- 407627-013 Model 3162A, 500MS/s Waveform Generator, w/4Meg RAM, 1PPM

- 407627-014 Model 3162A, 500MS/s Waveform Generator, w/8Meg RAM, 1PPM

- 407629-001 Model 3162B, 500MS/s Waveform Generator, w/1Meg RAM, 1PPM

1Meg RAM designates instruments supplied with the 1Meg memory. 1046464 point waveforms can be programmed. 4 Meg RAM designates 4193304 point waveforms and 8 Meg RAM designates 8387608 point waveforms can be programmed.

1ppm denotes the accuracy and stability grade of the internal 10MHz reference clock.

### **Manual Changes**

Technical corrections to this manual (if any) are noted on the pages themselves, with the change date shown at the bottom of the page..

### Safety Considerations

The Model 3162B has been manufactured according to international safety standards. The instrument meets VDE 0411/03.81 and UL 1244 standards for safety of commercial electronic measuring and test equipment for instruments with an exposed metal chassis that is directly connected to earth via the chassis power supply cable.

#### WARNING

Do not remove instrument covers when operating or when the chassis power cord is connected to the mains.

Any adjustment, maintenance and repair of an opened, powered-on instrument should be avoided as much as possible, but when necessary, should be carried out only by a skilled person who is aware of the hazard involved.

Revision 4/18/00

# Supplied Accessories

The instrument is supplied with an Instruction Manual. The manual includes disks with VXI plug&play drivers along with WaveCAD for Windows 3.1X and Windows 95/NT. A Service Manual is available upon request.

### **Specifications**

Instrument specifications are listed in Appendix A. These specifications are the performance standards or limits against which the instrument is tested. Specifications apply under the following conditions: output terminated into  $50\Omega$  after 30 minutes of warm up time, and within a temperature range of  $20^{\circ}$ C to  $30^{\circ}$ C. Specifications outside this range are degraded by 0.1% per  $^{\circ}$ C.

# Functional Description

A detailed functional description is given in the following paragraphs. The description is divided into logical groups: input and output connectors, operating modes, output type, output state, filters, synchronization, front panel indicators and programming.

# Input and Output Connectors

The Model 3162B has 7 BNC connectors on its front panel: two main outputs, SYNC output, TRIG/PLL/FSK input, channel A AM/PM input, channel B AM input and reference clock input. It also has a 9-pin D-sub connector for frequency hop and output segment control.

Figure 1-2, The Front Panel

# Main Output - Channel A

The main output A connector outputs standard, user, sequenced, and modulated waveforms. Output impedance is  $50\Omega$ . That is, the cable connected to this output should be terminated with  $50\Omega$ . Output amplitude accuracy is calibrated when connected to a  $50\Omega$  load. If the output is connected to a different load resistance, determine the actual amplitude from the following equation:

$$V_{\text{out}} = 2V_{\text{prog}} \left( \frac{50\Omega}{50\Omega + R_{\text{I}}} \right)$$

The output amplitude is doubled when the output impedance is above 1 M $\Omega$ .

# Main Output - Channel B

The main output B connector outputs standard, user, sequenced, and modulated waveforms. Phase offsets, accuracy and jitter are tightly controlled between the two main outputs. Main output B impedance is  $50\Omega$ . While amplitude, offset and waveform controls are separate for each channel, all other parameters are common (i.e., sample clock, trigger mode, etc.).

### **SYNC Output**

The SYNC output generates a single TTL pulse for synchronizing other instruments (e.g., an oscilloscope) to the output waveform. The SYNC signal always appears at a fixed point relative to the waveform. The location of the SYNC signal along the waveform is programmable.

# Trigger/PLL/FSK Input

The trigger input accepts signals that stimulate the Model 3162B to output waveforms. The trigger input is inactive when the instrument is in continuous operating mode. When placed in trigger, gated or burst mode, the trigger input is made active and waits for the right condition to trigger the instrument. In trigger and burst modes, the trigger input is edge sensitive, i.e., it senses transitions from high to low or from low to high to trigger the Model 3162B. The direction of the transition is programmable. In PLL mode, the trigger input is used as a phase reference input. In FSK mode, the trigger input is used as a frequency shift control. The FSK input is level sensitive, i.e., the Model 3162B outputs carrier frequency when the level is low and shifts to a pre-programmed frequency when the level is high. Trigger level sensitivity may be programmed for the trigger input.

In gated mode, the trigger input is level sensitive, i.e., the Model 3162B is gated when the a logic level is high and idle when it is low.

### AM/PM Input -

The channel A AM input accepts signals that amplitude modulate the channel A main output signal. The channel A PM Input accepts signals that phase

#### Channel A

modulate the channel A main output frequency. The phase modulation function operates in conjunction with the PLL function. The AM/PM input becomes active when one of these functions is selected.

#### **AM Input - Channel B**

The channel B AM input accepts signals that amplitude modulate the channel B main output signal. The AM input becomes active when one of these functions is selected.

# Reference Clock Input

The reference clock input accepts a 10 MHz, TTL level signal to replace the CLK10 reference. The reference clock input is active only when selected.

# Frequency/ Segment Control Input

The frequency and segment control input is a 9-pin, D-Sub type connector. Eight pins are used as control lines and one pin (pin 9) is connected to ground. The binary combination of pins 1 through 8 may be used to control 256 different frequency dividers, or 256 different segments. A frequency divider table and/or a segment table must first be loaded into the instrument before this input can modify the output. The signal level for this connector is TTL.

### **Operating Modes**

The Model 3162B can be programmed to operate in one of four operating modes: continuous, triggered, gated and counted burst. These modes are described below.

#### **Continuous Mode**

In normal continuous mode, the selected waveform shape is output continuously at the selected frequency, amplitude and offset.

### **Triggered Mode**

In triggered mode, the Model 3162B circuits are armed to generate one output waveform. The trigger circuit is sensitive to transitions at the trigger input. Select between positive or negative transitions to trigger the instrument. You may also program the trigger level to the desired threshold level. When triggered, the generator outputs one waveform cycle and remains idle at the last point of the waveform. The Model 3162B can be armed to receive a trigger signal from a front panel BNC connector, a VXI backplane TTLTRG<n> or ECLTRG0, or from an internal, programmable trigger generator.

The trigger signal, whether it comes from the front panel or from the VXIbus, has to pass through some electrical circuits. These circuits cause a small delay known as system delay. System delay cannot be eliminated completely. It is, however, minimized in the Model 3162B to approximately 100 ns maximum. System delay is a factor that must be considered when applying a trigger signal. It defines how long it will take from a valid trigger edge to the moment that the output reacts.

While system delay has a fixed value that cannot be controlled, the Model 3162B offers a controllable trigger delay parameter. When operated, delay from

a trigger signal to output waveform may be programmed from 0 clocks to 8 Million clocks. System delay factor must be added to your calculation of final delay value.

#### **Burst Mode**

The burst mode is an extension of the triggered mode where the Model 3162B can be armed to output a pre-determined number of waveforms. The source to trigger the counted burst cycle can be selected from a front panel BNC connector, VXI backplane trigger lines, or from the built-in trigger generator.

#### **Gated Mode**

In gated mode, the Model 3162B circuits are armed to generate output waveforms as long as a gating signal is true. Unlike the triggered mode, the gated mode is level sensitive. When the gating signal goes low, the waveform at the output connector is first completed and the output goes to an idle state. The idle amplitude level, after the gating signal goes low, is the last point on the waveform.

## **Output Type**

The Model 3162B can output three types of waveforms: standard (Fixed), arbitrary (User) and sequenced waveforms. The three types of waveforms are described in the following paragraphs.

# Standard (Fixed) Waveforms

The Model 3162B generates waveforms from a memory that must be loaded before the instrument can generate waveforms. There are 1Meg points available as standard. 2112 points from this memory are allocated for standard waveforms. Waveforms are loaded into this part of the memory each time that a standard function is selected.

The Model 3162B can be programmed to output ten different standard waveforms shapes: sine, triangle, square, pulse, ramp, sinc (sine(x)/x) pulse, gaussian pulse, exponential pulse, noise, and DC. There are a number of parameters associated with each waveform which modify the shape of the waveform to better suit your needs. For example, a different start phase for the sine waveform can be programmed for each channel to create phase offsets between the two output channels.

# Arbitrary (User) Waveforms

The arbitrary waveform memory is capable of storing one or more user-defined waveforms. There are 1,046,464 points that can be allocated to one waveform which has this length. There is no need to use the entire memory for one waveform. The memory can be divided into smaller segments, variable in size. The segments can be loaded with different waveforms and the Model 3162B can be programmed to output one segment at a time.

Loading data to arbitrary waveform memory can be a time-consuming task, especially if the complete 1Meg is loaded in one shot. The Model 3162B utilizes the VXIbus shared memory concept that speeds data transfer from and to the host computer. In this mode, the memory bank is disconnected from the

CPU circuit and re-routed to the bus on the backplane for direct memory access by the host computer.

The Model 3162B has separate arbitrary waveform memories for each channel. Each channel can be loaded with different waveforms. The only limitation is that if you divide channel A memory into smaller segments, the same divider is applied automatically to channel B.

# Sequenced Waveforms

The Model 3162B employs a sophisticated circuit that allows dividing the memory into smaller segments, linking of the segments in user-defined order, and repeating of each linked segment up to one million times. In addition, each segment can be programmed with a unique clock rate. The sequence circuit is useful for generating long waveforms with repeated sections. The repeated waveform has to be programmed once, and the repeater will loop on this segment as many times as selected. When in sequenced mode, there is no loss of time between linked or looped segments. Figure 1-6 shows an example of a sequenced waveform. Assume the waveforms in Figures 1-3 through 1-5 were placed in segments 1 through 3.

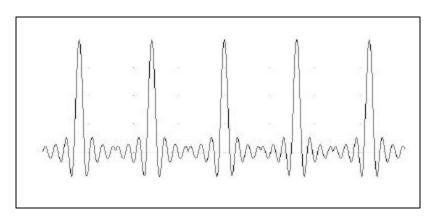

Figure 1-3, Segment 1 – Sin (x)/x Waveform

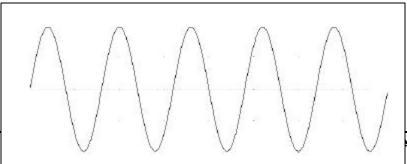

Figure 1-4, Segment 2 – Sine Waveform

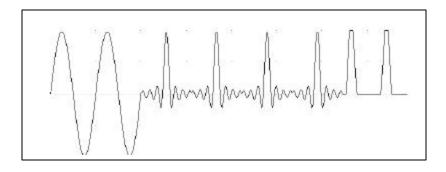

Figure 1-5. Segment 3 - Pulse Waveform

The following sequence was made of segment 2 repeated twice, segment 1 repeated four times, and segment 3 repeated two times.

Figure 1-6. Sequenced Waveforms

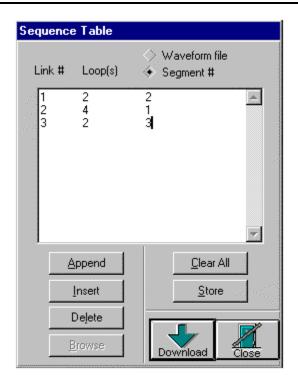

The table below, from WaveCAD's Sequence Table Editor, shows how the same sequence can be defined using WaveCAD.

Figure 1-7, WaveCAD Example

### Synthesizer Agility

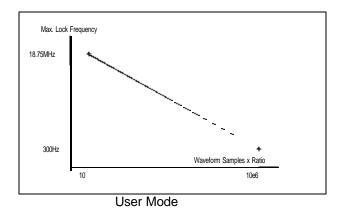

The Model 3162B is capable of frequency hopping, FSK modulation, and clock rate switching between memory segments. Frequency hopping is controlled from three different sources: front-panel 9 pin D-sub connector, front panel trigger input, and VXIbus trigger lines. The ratio between two frequencies is an integer number from 1 to 65536. The Model 3162B can hop between 256 predetermined frequencies.

In FSK modulation mode, the instrument outputs a carrier frequency as long as the control signal remains false. When the FSK control turns true, the generator outputs a shifted frequency signal which is an integer division of the carrier frequency. Frequency divider ranges from 1 to 65536.

In sequenced mode, clock frequency dividers may be assigned to each segment. The default divider is 1, while the maximum division ratio is 65536. The division ratio is stored in the clock divider segment assignment table. Every time a sequence runs, the clock rate is switched automatically and coherently to the assigned clock divider.

#### **Output State**

The main output can be turned on or off. The internal circuit is disconnected from the output BNC connector by a mechanical switch (relay). This feature is useful for connecting the Model 3162B main output, along with other instruments, to an analog bus. For safety reasons, when power is first applied to the chassis, the main output is always off.

# Amplitude Modulation

The Model 3162B may be amplitude modulated with an external signal. The amplitude modulation input accepts the envelope signal, while the carrier signal can be selected from any of the standard, user, or even sequenced waveforms. The frequency of the modulating signal ranges from DC to over 1 MHz. Each channel has separate amplitude modulation input.

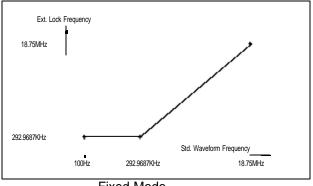

# Front-Panel / VXIbus PLL

Multiple Model 3162B s may be synchronized and operated together inside one VXIbus chassis. With one instrument configured as master and the rest of the instruments configured as slaves, the instruments are phase-locked to the start phase of the master module. Slave modules can be configured to have phase offsets from 0° to +360°. There is no need to install multiple Model 3162B modules into adjacent slots to phase synchronize modules.

The reference signal can be applied either to the front panel reference input or placed by one of the modules on one of the backplane trigger lines. This way, the same reference can be applied to all slave modules to generate phase-related signal patterns. The reference signal for the PLL function, when applied to the TRIG IN connector, shares the same characteristics as the trigger input: programmable trigger level and programmable slope.

When placed in PLL mode, the Model 3162B monitors the TRIG IN connector for valid signals. Once sensed, the Model 3162B measures the signal's

frequency and centers its lock-in range on this frequency. The Model 3162B then locks automatically onto the frequency of the external signal. There is no need for manual initiation or operator intervention to lock the instrument to an external reference.

#### **Frequency Counter**

The Model 3162B uses a built-in, auto-ranging counter circuit in PLL mode to measure the frequency of the reference signal at the trigger input. Regardless of whether you want to lock the 3162B to another source or not, you can use the counter circuit to measure frequency. There are three things to be done: 1) place the generator in PLL mode, 2) adjust the trigger level, and 3) make sure that the PLL ON LED illuminates. Frequencies are measured from 500Hz to 31 MHz. An external frequency query returns six digits with a decimal point and suffix multiplier.

#### **Phase Modulation**

When the Model 3162B is placed in PLL mode, there are two ways to control the phase offset. The first option is to modify the phase-offset setting using SCPI commands. This method is extremely accurate while permitting phase offset adjustments with 0.01° increments. The PM IN provides another option for changing phase offsets. This input is voltage sensitive. Applying voltage to this input changes the start phase of the generator. The bandwidth of the PM input is DC to 10kHz.

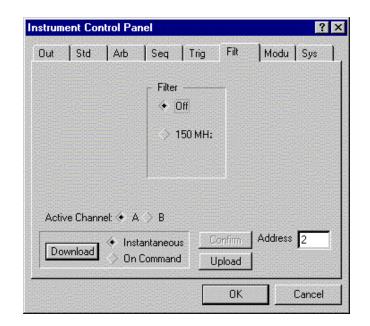

#### **Filters**

Two filters are built into the Model 3162B, one for each channel. These filters are available for use in various applications like the creation of high frequency sine waves. The elliptical 150 MHz filter has very sharp cutoff frequency. It is very useful for removing the staircase effect from waveforms that are generated with high frequency clock rates.

# Front Panel Indicators

There are five LED's on the front panel. The FAIL LED (Red) illuminates at power-up until the Model 3162B has passed self-test. If the Model 3162B self-test fails, the FAIL LED remains on.

The ACCESS LED (Amber) illuminates each time a command has been received by the Model 3162B. This light remains on during shared memory data transfer.

The PLL ON LED (Amber) is off during normal operation. In PLL mode, the PLL ON LED illuminates when a valid signal is available at the trigger input and lock frequency is available at the main output connector.

When the output state is on, the OUTPUT LED (Green) light illuminates. It goes off when the output state is changed to off. There is a separate LED for each channel.

# Programming The Model 3162B

The Model 3162B has no controls on its front panel. Instrument functions, parameters, and modes can only be accessed through VXIbus commands. There are a number of ways to talk to the instrument. They all require that an appropriate software driver be installed in the Resource Manager (slot 0). The rest is a matter of practice and knowledge of the language in use. There are other system considerations like address selection that have to be settled before programming the instrument. These topics are discussed in later chapters.

Low level programming of the Model 3162B is done using SCPI (Standard Commands for Programmable Instruments) language. Programming aspects are covered in Chapters 3 and 4.

High level drivers like VXI*plug&play* and WaveCAD are beyond the scope of this manual. Contact your Racal representative for more information about high level drivers for the Model 3162B.

This page was left intentionally blank.

### Chapter 2

### **CONFIGURING The INSTRUMENT**

### Installation Overview

This chapter contains information and instructions necessary to prepare the Model 3162A/B for operation. Details are provided for initial inspection, grounding safety requirements, repackaging instructions for storage or shipment, logical address selection and installation information.

# **Unpacking and Initial Inspection**

Unpacking and handling of the generator requires normal precautions and procedures applicable to the handling of sensitive electronic equipment. The contents of all shipping containers should be checked for included accessories and certified against the packing slip to determine that the shipment is complete.

### Safety Precautions

The following safety precautions should be observed before using this product and associated computer. Although some instruments and accessories would normally be used with non-hazardous voltages, there are situations where hazardous conditions may be present.

This product is intended for use by qualified persons who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. Read the operating information carefully before using the product.

Exercise extreme caution when a shock hazard is present. Lethal voltage may be present on cables, connector jacks, or test fixtures. The American National Standard Institute (ANSI) states that a shock hazard exists when voltage levels greater than 30V RMS, 42.4V peak or 60 VDC are present.

#### WARNING

For maximum safety, do not touch the product, test cables, or any other instrument parts while power is applied to the circuit under test. ALWAYS remove power from the entire

test system before connecting cables or jumpers, installing or removing cards from the computer, or making internal changes such as changing the module address.

Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always keep your hands dry while handling the instrument.

When using test fixtures, keep the lid closed while power is applied to the device under test. Carefully read the Safety Precautions instructions that are supplied with your test fixtures.

Before performing any maintenance, disconnect the line cord and all test cables. Only qualified service personnel should perform maintenance.

### Performance Checks

The instrument has been inspected for mechanical and electrical performance before shipment from the factory. It is free of physical defects and in perfect electrical order. Check the instrument for damage in transit and perform the procedures outlined in the section entitled **Unpacking and Initial Inspection**.

# **Grounding Requirements**

To ensure the safety of operating personnel, the U.S. <u>O.S.H.A.</u> (Occupational Safety and Health Administration) requirement and good engineering practice mandate that the instrument panel and enclosure be "earth" grounded. Although BNC housings are isolated from the front panel, the metal part is connected to earth ground.

#### WARNING

Do not attempt to float the output from ground, as it may damage the Model 3162A/B and your equipment.

### Long Term Storage or Repackaging For Shipment

If the instrument is to be stored for a long period of time or shipped immediately, proceed as directed below. If you have any questions, contact your local Racal Instruments Representative or the Racal Instruments Customer Service Department.

- 1. Repack the instrument using the wrappings, packing material and accessories originally shipped with the unit. If the original container is not available, purchase replacement materials.

- 2. Be sure the carton is well sealed with strong tape or metal straps.

3. Mark the carton with the model and serial number. If it is to be shipped, show sending and return address on two sides of the box.

#### NOTE

If the instrument is to be shipped to Racal Instruments for calibration or repair, attach a tag to the instrument identifying the owner. Note the problem, symptoms, and service or repair desired. Record the model and serial number of the instrument. Show the work authorization order as well as the date and method of shipment. ALWAYS OBTAIN A RETURN AUTHORIZATION NUMBER FROM THE FACTORY BEFORE SHIPPING THE INSTRUMENT TO RACAL INSTRUMENTS.

#### **Preparation For Use**

Preparation for use includes removing the instrument from the container, selecting the required logical address and installing the module in a VXIbus chassis.

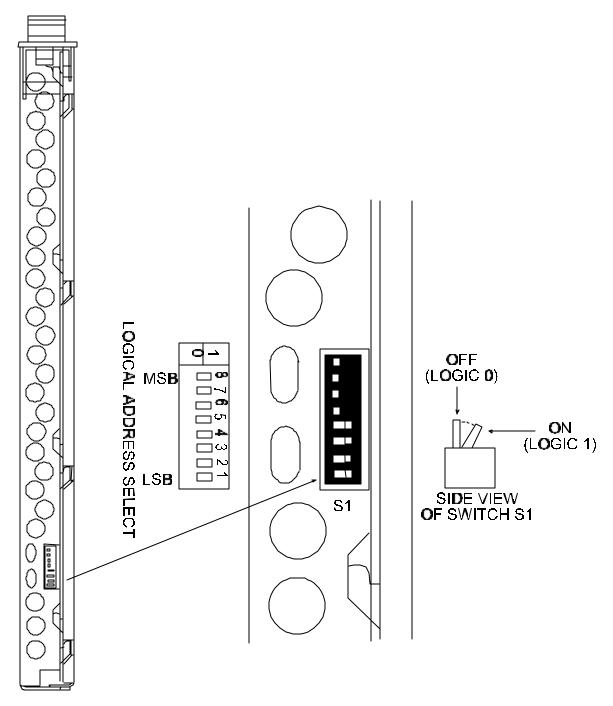

# Logical Address Selection

The VXIbus Resource Manager identifies modules in the system by the module s address. VXIbus logical addresses can range from 0 to 255, however, addresses 1 to 254 **only** are reserved for VXIbus modules. Logical address 0 is reserved for the Resource Manager. Logical address 255 permits the Resource Manager to dynamically configure the module logical address.

To change the logical address, use the 8-position DIP switch accessible from the top side of the module near the rear end of the case (switch S1). Figure 2-1 shows the location of the logical address switch. The switches are marked with numbers 1 to 8. The Model 3162A/B uses binary values ( $2^0$  to  $2^7$ ) to set the logical address using the active low address switch. A switch is active when its arm is placed in the ON position.

Racal Instruments ships the Model 3162A/B with logical address 2.

Figure 2-1, Set Logical Address

### Installation

The instrument can be installed in any slot except slot 0 in a VXIbus mainframe. When inserting the instrument into the mainframe, it should be gently rocked back and forth to seat the connectors into the backplane receptacle. The ejectors will be at right angles to the front panel when the instrument is properly seated into the backplane. Use two captive screws

| above and below the ejectors to secure the instrument into the chassis.  After installation, perform an initial checkout and operational verification. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

|                                                                                                                                                        |

# Chapter 3 USING THE INSTRUMENT

#### Overview

This chapter contains information about how to operate the Model 3162A/B. Unlike bench-type instruments, the Model 3162A/B must be programmed to turn on functions, change parameters and configure various operating modes. Two graphical interfaces are available for programming the instrument: VXlbus*plug&play* and WaveCAD. LabWindows/CVI drivers and a set of SCPI commands are available for experienced programmers. SCPI (Standard Commands for Programmable Instruments) commands for the Model 3162A/B are listed in Table 4-1. This manual provides information on low-level programming using SCPI commands only. The following paragraphs describe the various modes of operation and give examples of how to program the Model 3162A/B.

#### NOTE

The Model 3162B has the same functionality as the Model 3162A. This manual describes all functions and feature that are available on the Model 3162B. If you own the Model 3162A, simply ignore all references in this chapter to the second output channel.

# Inter-Channel Dependency

The Model 3162B has two output channels. Although this is a two-channel instrument, most of the commands that set parameters and functions are common for both channels. For example, sample clock and trigger modes cannot be set separately for each channel. On the other hand, you may program each channel to have a different function shape, amplitude and offset. Table 3-1 lists the functions and parameters and their related inter-channel dependency.

### Output Termination

During use, output connectors must be properly terminated to minimize signal reflection or power loss due to an impedance mismatch. Proper termination is also required for an accurate amplitude level at the main output connector. Use  $50\Omega$  cables and terminate the main and SYNC cables with terminating resistors. Always place the  $50\Omega$  termination at the far end of each cable.

### Input/Output

The Model 3162B provides protection for internal circuitry connected to input and output connectors. Refer to the specifications in Appendix A to determine

#### **Protection**

the level of protection associated with each input or output connector.

# Power On/Reset Defaults

At Power On or as a result of a software reset, the Model 3162B defaults to the conditions shown in Table 3-1. Also listed in this table are parameters that are common or separate for each channel. A complete list of all parameters, their default values, as well as their maximum and minimum values is given in Chapter 4.

Use the following command to place the instrument in its default state:

RESet;

Using the IEEE-STD-488.2 common command \*RST will have the same result.

| Function / Parameter     | Default    | Inter-Channel<br>Dependency |

|--------------------------|------------|-----------------------------|

| Output State:            | Off        | Separate                    |

| Operating Mode:          | Continuous | Common                      |

| SYNC State:              | Off        | Common                      |

| SYNC Out Position:       | Wave Start | Common                      |

| Output Function:         | Standard   | Separate                    |

| Output Function Shape:   | Sine       | Separate                    |

| Standard Wave Frequency: | 1MHz       | Common                      |

| User Wave Sample Clock:  | 1MHz       | Common                      |

| Amplitude:               | 2V         | Separate                    |

| Offset:                  | OV         | Separate                    |

| Filter State:            | Off        | Separate                    |

| Filter Type:             | Auto       | Separate                    |

| ECLTRG0:                 | Off        | Common                      |

| TTLTRG0-3:               | Off        | Common                      |

Table 3-1, Default Conditions After Power On or After \*RST

| Function / Parameter     | Default  | Inter-Channel<br>Dependency |

|--------------------------|----------|-----------------------------|

| Trigger Slope:           | Positive | Common                      |

| Trigger Level:           | 1.6 V    | Common                      |

| Internal Trigger Period: | 100 μs   | Common                      |

| PLL State:               | Off      | Common                      |

| AM State:                | Off      | Separate                    |

| Shared Memory State:     | Off      | Separate                    |

| Shared Memory Mode:      | Write    | Separate                    |

Table 3-1, Default Conditions After Power On or After \*RST (continued)

### What To Do Now

When writing low level code to operate the Model 3162B, follow the instructions in this chapter to understand the meaning and response that each command generates. Examples contained in the following paragraphs show basic techniques of how to program output waveforms.

#### Example 1

The following example programs the Model 3162B to turn on the main outputs and program the waveform frequency to 20 MHz. It programs channel A to output a square waveform with an amplitude of 2V and offset of 0.5V, and programs channel B to output a triangular waveform with an amplitude of 1V and offset of 0.5V.

/\* Reset the Model 3162B to its default condition as listed in Table 3-1. \*/

:RESet;

/\* Change the output waveform to square. Note that there is no need to use the FUNC:MODE command as the default value after RESet is FIXed. \*/

:FUNCtion:SHAPe SQUare;

/\* Change the frequency to 20MHz. Note that the frequency setting is common for both channels. \*/

:FREQuency 20e6;

/\* Change channel A amplitude to 2V and the offset to 0.5V. \*/

:VOLTage 2;

:VOLTage: OFFSet 0.5;

Note that output peak voltage may never exceed  $\pm 2.5$ V. Amplitude and offset may be set freely within a 5V window, as long as the following limits are kept:

```

| offset | + Vp-p \div 2 \leq 5

```

/\* Turn on channel A main output. \*/

:OUTPut ON;

/\* Turn on the SYNC output, if required. \*/

:OUTPut:SYNC ON;

If the above commands are executed correctly, a square waveform will be seen on your oscilloscope at the channel A output connector.

So far, there was no need to specify which of the channels is receiving commands for two reasons: 1) channel A is the default channel and 2) the frequency parameter is common to both channels. Common parameters affect the two channels the same way. For example, changing the frequency for channel A will automatically change the frequency for channel B. This example will now continue with programming the channel B parameters.

/\* The following command changes control to the B channel. \*/

:INSTrument:SELect B;

/\* Change channel B amplitude to 1V and the offset to 0.5V. \*/

:VOLTage 1;

:VOLTage: OFFSet 0.5;

/\* Turn on channel B main output. \*/

:OUTPut ON;

/\* Turn on the SYNC output, if required. \*/

:OUTPut:SYNC ON;

If the above commands are executed correctly, a square waveform will be seen on your oscilloscope at channel B output connector.

## Using the APPLy Command

The APPLy command provides a high level method of programming the generator. Selection can be made for function, frequency, amplitude, offset and other parameters which are associated with the applied function. For example, the following statement outputs a 2Vp-p square wave at 1 MHz with a 0V offset and 10% duty cycle using APPLy:

APPL:SQU 1E6, 2, 0, 10

It is not necessary to enter every parameter with the APPLy command. If only the frequency and offset need to be changed, omit the other parameters while keeping the commas. The other parameters will be set to the power-up default values:

```

APPL:SQU 10E6,,1

```

Alternatively, if just the first parameters need to be changed, omit the commas. The other parameters will be set to the power-up default values:

```

APPL:SQU 4e6,2

```

Queries can also be made on all parameters associated with a standard function using the APPL: <function\_shape>? query. For example, if the generator was programmed using the above APPLy:SQU command, query the square wave parameters using the following query:

```

APPL:SQU?

```

The generator returns a string that contains all the parameters associated with the square function similar to the following string:

```

"1.000000e+6,2.000,0.000,50"

```

The command:

```

APPLy:SINusoid {<frequency>,<amplitude>,<offset>,<phase>,<power>}

```

programs the generator to output a sine waveform with frequency, amplitude, offset, start phase and power parameters. Parameters are not optional if the above APPLy command is used. Include all other parameters in the command. The default settings for these parameters are: 1MHz, 2Vp-p, 0V, 0 and 1.

The command:

```

APPLy:TRlangle {<frequency>,<amplitude>,<offset>,<phase>,<power>}

```

programs the generator to output a triangle waveform with frequency, amplitude, offset, start phase, and power parameters. The default settings for these parameters are: 1 MHz, 2Vp-p, 0V, 0 and 1.

The command:

```

APPLy:SQUare {<frequency>,<amplitude>,<offset>,<duty_cycle>}

```

programs the generator to output a square waveform with frequency, amplitude, offset and duty cycle parameters. The default settings for these parameters are: 1MHz, 2Vp-p, 0V, and 50%.

The command:

```

APPLy:PULSe{<frequency>,<amplitude>,<offset>,<delay>,<high_time>,<rise_time>,<fall_time>}

```

programs the generator to output a pulse waveform with frequency, amplitude,

offset, delay, high time, rise time, and fall time parameters. The default settings for these parameters are: 1MHz, 2Vp-p, 0V, 0%, 10%, 10% and 10%.

#### The command:

```

APPLy:RAMP {<frequency>,<amplitude>,<offset>,<delay>,<rise_time>,<fall_time>}

```

programs the generator to output a ramp waveform with frequency, amplitude, offset, delay, rise time, and fall time parameters. The default settings for these parameters are: 1MHz, 2Vp-p, 0V, 0%, 10% and 10%.

#### The command:

```

APPLy:SINC {<frequency>,<amplitude>,<offset>,<number_cycles>}

```

programs the generator to output a sine(x)/x waveform with frequency, amplitude, offset, and number of cycles parameters. The default settings for these parameters are: 1MHz, 2Vp-p, 0V and 10.

#### The command:

```

APPLy:EXPonential <frequency>,<amplitude>,<offset>,<exponent>}

```

programs the generator to output an exponential waveform with frequency, amplitude, offset, and exponent parameters. The default settings for these parameters are: 1MHz, 2Vp-p, 0V and -10.

#### The command:

```

APPLy:GAUSsian {<frequency>,<amplitude>,<offset>,<exponent>}

```

programs the generator to output a gaussian waveform with frequency, amplitude, offset, and exponent parameters. The default settings for these parameters are: 1MHz, 2Vp-p, 0V and 10.

#### The command:

```

APPLy:DC {<percent amplitude>}

```

programs the generator to output a DC level. The DC level is set as a percent of programmed amplitude. The default setting for this function is 100%.

#### The command:

```

APPLy:USER {<segment_number>,<sampling_clock>,<amplitude>,<offset>}

```

programs the generator to output an arbitrary waveform. The specified segment number must be loaded with an arbitrary waveform before the generator can execute this command successfully. This command lets you specify segment number, sampling clock rate, amplitude and offset. The default settings for these parameters are: 1, 1MHz, 2Vp-p and 0V.

The query:

APPLy:<function\_shape>?

queries parameters associated with the specified function shape, and returns a string of values depending on the parameters that are available for the selected function shape.

The query:

APPLy?

queries parameters associated with the currently selected function shape and returns a string of values depending on the parameters available for the selected function shape. For example, if the generator is programmed to output a ramp waveform, the APPL? command returns: "1e+6, 2, 0, 0, 10, 10, 10".

#### Example 2

The following example programs the Model 3162B using the APPLy command. This example turns on the main output, generates a square waveform, programs frequency to 2MHz, programs amplitude to 1V and offset to 1V. It also changes the square wave duty cycle parameter to 25%.

/\* Reset the Model 3162B to its default condition as listed in Table 3-1. \*/

:RESet;

/\* Change the output waveform to square, frequency to 2MHz, amplitude to 1V, offset to 1V and duty cycle to 25%. Note that there is no need to use the FUNC:MODE command because the default value after RESet is FIXed. \*/

:APPLy:SQUare 2e6,1,1,25

/\* Turn the main output on. \*/

:OUTPut ON

/\*Turn the SYNC output on, if required. \*/

:OUTPut:SYNC ON

If the above commands are executed correctly, a square waveform will be seen on your oscilloscope.

## Selecting the Active Channel

Use the following command to select the active channel:

INSTrument:SELect {A | B}

When "A" is selected, commands will control parameters that are unique for the channel A output. Selecting "B", modifies the control of channel B parameters. The default option is "A". Parameters that are common to both channels may be programmed from either path.

The query:

**INSTrument:SELect?**

queries the active channel and returns A or B.

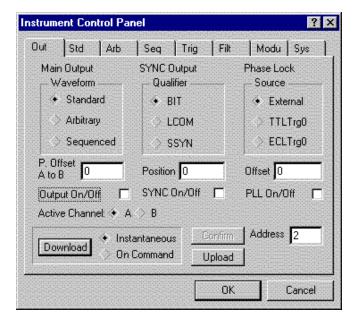

## Output Configuration Commands

The output configuration commands control the output function, shape, frequency, amplitude, filter and state. Optional modes are omitted from these commands. The Output Instrument Control Panel from WaveCAD is shown below as an example of high-level implementation of output control.

Figure 3-1, Output Control with a WaveCAD Panel

## Selecting an Output Function Type

Use the following command to select the output function type:

FUNCtion: MODE {FIXed | USER | SEQuence}

When "FIXed" is selected, the generator outputs the standard waveform currently selected by the FUNC:SHAP command. When "USER" is selected, the generator outputs the arbitrary waveform currently selected by the TRAC:SEL command. When "SEQuence" is selected, the generator outputs the sequence that is programmed using the SEQ:DEF command.

The query:

FUNCtion:MODE?

queries the output function type and returns FIX, USER or SEQ.

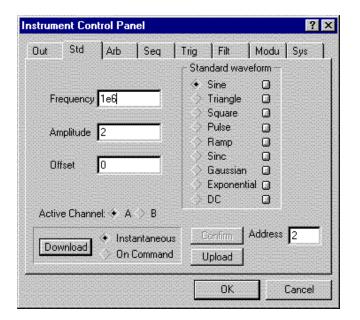

## Selecting a Standard Function Shape

Use the following command to select a standard output function:

FUNCtion:SHAPe {SINusoid | TRlangle | SQUare | PULSe | RAMP | SINC | EXPonential | GAUSsian | NOISe | DC}

The selected waveform is output using the previously selected frequency, amplitude, offset, and other relevant settings. The standard waveform will be output only after the FUNC:MODE:FIX command is selected.

The query:

FUNCtion:SHAPe?

queries the standard function shape and returns either SIN, TRI, SQU, PULS, RAMP, SINC, EXP, GAUS, NOIS or DC.

The Standard Waveform Instrument Control Panel from WaveCAD is shown below as an example of a high-level implementation of Standard Waveform Selection.

Figure 3-2, Standard Waveform Selection Panel from WaveCAD

### Changing the Frequency and Sample Clock

Use the following command to change the frequency for standard waveforms:

FREQuency {<frequency> | MINimum | MAXimum}

MIN selects the lowest frequency allowed for the currently active function. MAX selects the highest frequency allowed for the currently active function. The default frequency setting is 1 MHz for all parameters.

The query:

FREQuency?

queries the frequency setting for the standard function currently active and returns a value in hertz.

The command:

FREQuency:RASTer {<frequency> | MINimum |MAXimum}

sets the sample clock frequency for the user and sequenced mode parameters. MIN selects the lowest frequency allowed for the currently active segment or sequence. MAX selects the highest frequency allowed for the currently active segment or sequence. The default sample clock frequency setting is 1 MHz for all parameters.

Note that the output frequency depends on the number of points specified in the waveform. The output frequency can be computed using the following formula: Output Frequency = Sample Clock / Number of points in the active segment.

The query:

FREQuency:RASTer?

queries the sample clock frequency setting for the arbitrary segment or sequence currently active and returns a value in Hertz.

## Controlling Synthesizer Agility

Use the following commands to select the control mode for the frequency synthesizer:

FREQuency: MODE {NORMal | FSK | HOP}

In NORM mode, the selected output function is generated continuously with the programmed frequency parameter. FSK places the Model 3162B in frequency shift keying FSK mode. HOP selects frequency-hopping mode, where the generator can hop between various frequencies, as programmed in the hop table.

The query:

#### FREQuency:MODE?

queries the frequency mode setting and returns NORM, FSK or HOP.

#### **FSK Mode**

In FSK mode, the generator outputs a pre-selected waveform with the frequency or sample clock setting as carrier frequency, as long as the controlling line remains false (logic zero). Toggling the controlling line true (logic one) modifies the output frequency to another frequency, which is determined by a pre-programmed dividing ratio. Use the following command to program the FSK dividing ratio:

FREQ:FSK<dividing\_ratio>

The dividing ratio must be an integer number from 1 to 65536. The default value is 1.

The query:

FREQ:FSK?

queries the FSK dividing ratio and returns an integer value.

FSK control is available from a number of sources. Use the following command to select FSK control source:

FREQ:FSK:SOURce {EXTernal | TTLTrg<0-3> | ECLTrg0}

EXT selects the front panel TRIG IN connector as the FSK control source. First program the trigger level and slope of the trigger input, then apply the control signal. Information on how to program the trigger level is given later in this chapter.

When a positive trigger slope is selected for the trigger level input (default), signal levels below the programmed trigger level are false (carrier frequency). Signal levels above the programmed trigger level are true and shift the carrier frequency to the modulated frequency. Changing the trigger slope to negative inverts the above conditions.

The default trigger level is 1.6 V. This is convenient for TTL level control. You may change the trigger level setting if your signal is not TTL.

TTLT<n> or ECLT0 select the VXIbus backplane as FSK control source. For TTLT<n> or ECLT0, a logic low generates the carrier frequency. A logic high level at these lines generates the shifted frequency.

The query:

FREQ:FSK:SOURce?

queries the FSK control source and returns EXT, TTLT<n> or ECLT0.

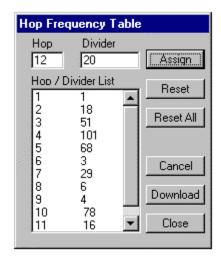

#### **HOP Mode**

In HOP mode, the generator outputs a pre-selected waveform whose frequency (or sample clock setting) is determined by the HOP table and HOP control lines. The Model 3162B hops from frequency to frequency according to a predetermined table. The hop table contains hop numbers and their associated dividing ratios. The hop table holds up to 256 hop settings.

The WaveCAD Hop Table editor (shown below) is an example of a graphical interface for defining a hop table.

Figure 3-3, WaveCAD Hop Table

The following low-level commands programs a five-step hop table:

FREQ:HOP 1,50 FREQ:HOP 2,500 FREQ:HOP 3,5000 FREQ:HOP 4,50000

Each trigger advances the output to the next frequency. In the above example, setting the sample clock to 200MHz generates the following hop frequencies: 200MHz, 40MHz, 40MHz, 400kHz, and 40kHz. If the trigger lines are used as the hop advance sources, the sequence will repeat itself continuously. By selecting the D-Sub connector as the hop advance source, any external hop pattern may be used. Undefined hop table entries have a dividing ratio of 1.

Note that the hop command does not have a query.

The command:

#### FREQ:HOP:SOURce {EXTernal | TTLTrg<0-3> | ECLTrg0 | DSUB}

selects the hop advance source. EXT selects the front-panel TRIG IN connector. Every valid trigger signal increments the table to the next step. TTLT<n> or ECLT0 select the corresponding VXIbus backplane trigger line.

A front-panel D-Sub connector is selected as the hop advance source when the DSUB option is selected. This connector has 9 pins, of which one (pin 9) is connected to ground and the other 8 pins are used as advance control lines. The binary value of these 8 lines determines the next hop step. For example, when none of the pins are connected to an external +5V signal, the generator outputs its carrier frequency. If pins 1 and 2 are connected to an external +5V signal, the output hops to the frequency set by step Hop Table entry number 3

The query:

FREQ:HOP:SOURce?

queries the hop frequency advance source and returns either EXT, TTLT<n>, ECLT0 or DSUB.

The command:

FREQ:HOP:DELete<n>

deletes the specified hop steps from the hop table.

The command:

FREQ:HOP:DELete:ALL

deletes all hop steps and resets the hop table.

### Selecting the Reference Oscillator

Use the following command to select the reference oscillator for the synthesizer circuit:

ROSCillator:SOURce {CLK10 | EXTernal | TCXO}

TCXO is the standard reference oscillator for the Model 3162B. The default reference oscillator is set to TCXO. Regardless, you can still select and use other reference sources. CLK10 accuracy is 100ppm and TCXO accuracy is 1ppm. If you have a 10MHz signal that is either more stable or is shared with other system modules, you can apply it to the front panel reference input. CLK10 connects the VXIbus backplane clock to the internal synthesizer circuit. EXT connects the front panel TTLreference input to the main clock circuit.

The query:

ROSCillator:SOURce? {CLK10 | EXTernal | TCXO}

queries the reference oscillator source and returns either CLK10, EXT or TCXO.

### Programming the Output Amplitude and Offset

Use the following command to program the peak-to-peak amplitude of the generated waveform:

VOLTage {<amplitude>|MINimum|MAXimum}.

MIN selects the smallest possible amplitude. MAX selects the largest possible amplitude. The default amplitude is 2.00V (into  $50\Omega$ ).

The query:

VOLTage?

queries the output amplitude and returns a value in volts.

The command:

VOLTage:OFFSet <offset>

sets the offset. The default offset is 0V.

The query:

VOLTage:OFFSet?

queries the output offset and returns a value in volts.

### Selecting the Filter

Use the following command to activate the filter:

OUTPut:FILTer { OFF | ON}

The 3162B has a seven-pole, built-in 150MHz filter, with elliptical characteristic and very sharp cutoff frequency. This filter is used for generating the sine waveforms and, when in other output functions, can be used for other filtering tasks. ON enables the filter. The default filter state setting is OFF.

Note

The default output function of the generator is the sine waveform. Since the instrument uses the filter to generate this waveform, the state of the OUTP:FILT cannot be changed until another output function is selected. A setting conflict error will occur if one attempts to change the filter state before changing to another output function or mode.

The WaveCAD Filter Control Panel is shown below as a graphical implementation of the filter setting.

Figure 3-4, WaveCAD FilterControl Panel

The query:

OUTPut:FILTer?

queries the output filter state and returns "0" (OFF) or "1" (ON).

### Activating the Backplane ECLTRG and TTLTRG Lines

The Model 3162B can transmit and receive signals on VXIbus ECLTRG line zero and TTLTRG lines zero through three.

Use the following command to activate one of two backplane ECLTRG lines:

OUTPut:ECLTrg0 { OFF | ON}

ON enables the ECL trigger line. The trigger source for this line can be selected with the TRIG:SOUR command. The default ECLTrg0 state is OFF. Note that the trigger validation source for ECLT0 is exactly as was set for the SYNC output.

The query:

OUTPut:ECLTrg0?

queries the ECLTrg0 state and returns "0,0" (OFF) or "0,1" (ON).

TTLTRG lines zero through three can be used to transmit and receive trigger signals between the Model 3162B and other VXIbus modules.

Use the following command to activate one of the four backplane TTLTRG lines:

OUTPut:TTLTrg<n> { OFF | ON}

where <n> designates the activated trigger line and 0 through 3 are available. ON enables the selected trigger line. Note that the trigger validation source for TTLT<n> is exactly as was set for the SYNC output.

The query:

OUTPut:TTLTrg<n>?

queries the TTLTRG<n> state and returns "<n>,0" (OFF) or "<n>,1" (ON).

## Enabling the Main Output

For safety reasons, the main output default setting is OFF. Disable or enable the main output using the following command:

OUTPut {OFF | ON}

When the main output state is programmed to ON, the output connector is connected to the output amplifier through a  $50\Omega$  resistor. In the OFF position, the output connector is disconnected from the output amplifier by means of a mechanical relay. Ensure that voltage is **not** applied to the main output connector when the Model 3162B output state is programmed to ON.

The query:

**OUTPut?**

queries the state of the main output and returns "0" (OFF) or "1" (ON).

## Enabling the SYNC Output